|

|

|

|

Microcontrolador

|

|

|

Capítulo

I

Justificación y detalles.

A estas

alturas no

es necesario

hacer la presentación de éste tipo de

componentes, que llevan ya muchos años, desde la

década de los ochenta, introducidos en el mundo

electrónico y en la vida cotidiana.

No vamos pues a entrar en su utilidad, sino que nos

ceñiremos a nuestra aplicación y su actividad en

ella.

|

|

| |

Las necesidades de control de

nuestro sistema son las siguientes:

* Un puerto paralelo de ocho bits,

de comunicación con el MPID.

* Señales de control para el MPID, en concreto:

* Selección del periférico, "Chip select", CS.

* Señal de aviso de lectura, RD.

* Señal de aviso de escritura, WR.

* Selección de uso del puerto de comunicaciones para datos o

instrucciones del MPID, PS.

* Reloj que se enviará al MPID, CLKp.

* Línea de recepción de interrupciones generadas

por el MPID.

* Línea de RESET "hardware" del MPID.

* Línea de recepción de interrupciones generadas

por el puente H.

* Líneas de información de datos aportados por el

puente H.

Las capacidades que precisaremos del µC van a ser:

* Velocidad, reloj, superior a 8 Mhz, dado que ésta va a ser

la velocidad del MPID.

* Dos puertos paralelo de 8 bits mínimo, uno para la

comunicación con el PID y el otro para señales de

control.

* Memorias RAM y ROM. No se considera necesario ampliar la memoria.

* Puerto serie para comunicación con el exterior del sistema.

* Memoria EPROM para su uso en la comunicación con el

exterior del sistema.

Son muchos los microcontroladores que actualmente cumplen estos

requisitos mínimos y diversas las casas que los fabrican.

Existen, además de los microcontroladores

clásicos, los DSP (Digital Signal Proccessing), cuya

arquitectura interna difiere del µC con objeto de agilizar la

comunicación, para el trabajo en tiempo real, pero en

nuestro caso esta actividad la llevará a cabo el MPID, por

tanto el µC es adecuado y suficiente.

Fabricantes de referencia en este campo son "Motorola" e "Intel". Se ha

buscado información de ambas casas, teniendo ofertas

similares. En concreto, y aunque se ha optado por la familia 8051 de

"Intel", se estudió la familia 68HC11 de "Motorola", que

aporta en su modelo MC68HC11F1 un convertidor analógico

digital (ADC) interno de 8 bits que pudiera resultar útil en

el manejo de datos analógicos procedentes del puente H.

Pero esto se va a resolver en forma diferente, y por otro lado en la

comparativa de velocidades del reloj, la oferta de la familia 8051 es

más ventajosa.

No podemos obviar tampoco que la información disponible de

la familia 8051 ha sido mayor, siendo muy utilizados y muy estudiados.

Por tanto hemos optado por un sistema ya conocido y ampliamente

experimentado.

La elección del modelo, con arreglo a las necesidades dio

como resultado el uso del 87C51RC, encapsulado DIP, con 40 contactos.

Sin embargo, y como era de esperar, al recabar información

en la página "web" de Intel, encontramos la

última actualización de la familia, los 8XC251XX,

que prometen compatibilidad "hardware" y "software" con la primitiva

MCS51, mejorando aspectos externos e internos. El encapsulado es de 44

pines, PLCC, puesto que no es preciso mantener compatibilidad. Aunque

no es objeto del trabajo, en paralelo con la descripción del

nuevo modelo seleccionado incluimos datos del antiguo en plan

comparativo.

El modelo seleccionado, equivalente al 87C51RS va a ser el 87C251SB de

la misma casa Intel. Entre corchetes [x], se incluyen las diferencias,

cuando las hay, con el antiguo modelo.

Sus características generales son:

* 1 K Byte de memoria RAM. [512 bytes]

* 16 K ROM / OTPROM / EPROM. [32K]

* Reloj (CLK) de 16 Mhz. [12 Mhz]

* 4 puertos paralelo bidireccionales de 8 bits.

* 3 contadores de 16 bits con:

1 contador arriba / abajo

Salida de reloj

* Puerto serie programable "Full Duplex"

* Set de instrucciones ampliado

* 3 contadores de 16 bits

* Estructura de Interrupciones

Siete fuentes de interrupción

Cuatro niveles de prioridad

* Vigilante Watchdog hardware

* Reducción de consumo tipos "idle" y "power down".

* Más detalles en las características del

fabricante.

|

|

|

|

|

|

µC 87C251SB.

DESCRIPCIÓN DE PATILLAS

|

|

|

"Pin

out"detallado del Microcontrolador 87C251SB

|

|

|

| PIN

|

SIGNO

|

DESCRIPCIÓN |

ALTERNATIVA |

| 01 |

VSS1 |

ALIMENTACIÓN |

|

| 02 |

P1.0 |

PUERTO 1.0 |

T2 |

|

| 03 |

P1.1 |

PUERTO 1.1 |

T2EX |

|

| 04 |

P1.2 |

PUERTO

1.2 |

ECI |

|

| 05 |

P1.3 |

PUERTO

1.3 |

CEXO |

|

| 06 |

P1.4 |

PUERTO 1.4 |

CEX1 |

|

| 07 |

P1.5 |

PUERTO 1.5 |

CEX2 |

|

| 08 |

P1.6 |

PUERTO

1.6 |

CEX3 |

WAIT

# |

|

| 09 |

P1.7 |

PUERTO 1.7 |

CEX4 |

A17 |

WCLK |

|

| 10 |

RST |

RESET |

|

| 11 |

P3.0 |

PUERTO

3.0. |

RECEPCIÓN

SERIE |

RXD |

| 12 |

VCC2 |

ALIMENTACIÓN |

|

| 13 |

P3.1 |

PUERTO 3.1 |

TRANSMISIÓN

SERIE |

TXD |

| 14 |

P3.2 |

PUERTO 3.2 |

INTERRUPCION

0 |

/INT0 |

| 15 |

P3.3 |

PUERTO 3.3 |

INTERRUPCION

1 |

/INT1 |

| 16 |

P3.4 |

PUERTO 3.4 |

TIMER 0 |

T0 |

| 17 |

P3.5 |

PUERTO

3.5 |

TIMER 1 |

T1 |

| 18 |

P3.6 |

PUERTO

3.6 |

ESCRITURA |

/WR |

| 19 |

P3.7 |

PUERTO

3.7 |

LECTURA |

A16 |

/RD |

| 20 |

XTAL2 |

CRISTAL

DE RELOJ EXTERNO. ENTRADA |

|

| 21 |

XTAL1 |

CRISTAL

DE RELOJ EXTERNO. COMÚN |

|

| 22 |

VSS |

COMÚN

ALIMENTACIÓN |

|

| 23 |

VSS2 |

|

|

| 24 |

P2.0 |

PUERTO 2.0 |

DIRECCIÓN

ALTA 8 |

A8 |

| 25 |

P2.1 |

PUERTO 2.1 |

DIRECCIÓN

ALTA 9 |

A9 |

| 26 |

P2.2 |

PUERTO 2.2 |

DIRECCIÓN

ALTA 10 |

A10 |

| 27 |

P2.3 |

PUERTO 2.3 |

DIRECCIÓN

ALTA 11 |

A11 |

| 28 |

P2.4 |

PUERTO 2.4 |

DIRECCIÓN

ALTA 12 |

A12 |

| 29 |

P2.5 |

PUERTO 2.5 |

DIRECCIÓN

ALTA 13 |

A13 |

| 30 |

P2.6 |

PUERTO

2.6 |

DIRECCIÓN

ALTA 14 |

A14 |

| 31 |

P2.7 |

PUERTO 2.7 |

DIRECCIÓN

ALTA 15 |

A15 |

| 32 |

/PSEN |

STROBE

MEMORIA EXTERNA |

|

| 33 |

ALE |

HABILITA

LATCH DIRECCIONES / ENTRADA PROGRAMACIÓN EPROM |

/PROG |

| 34 |

VSS2 |

|

|

| 35 |

/EA |

HABILITA

ACCESO EXTERNO / ALIMENTACIÓN PROGRAMACIÓN EPROM |

VPP |

| 36 |

P0.7 |

PUERTO 0.7 |

DIRECCIÓN

BAJA 7 |

AD7 |

| 37 |

P0.6 |

PUERTO 0.6 |

DIRECCIÓN

BAJA 6 |

AD6 |

| 38 |

P0.5 |

PUERTO 0.5 |

DIRECCION

BAJA 5 |

AD5 |

| 39 |

P0.4 |

PUERTO

0.4 |

DIRECCIÓN

BAJA 4 |

AD4 |

| 40 |

P0.3 |

PUERTO 0.3 |

DIRECCION

BAJA 3 |

AD3 |

| 41 |

P0.2 |

PUERTO

0.2 |

DIRECCION

BAJA 2 |

AD2 |

| 42 |

P0.1 |

PUERTO 0.1 |

DIRECCION

BAJA 1 |

AD1 |

| 43 |

P0.0 |

PUERTO 0.0 |

DIRECCION

BAJA 0 |

AD0 |

| 44 |

VCC |

ALIMENTACIÓN

POSITIVA |

|

|

|

|

µC 87C251SB.

DESCRIPCIÓN DE PATILLAS |

|

|

|

|

|

|

|

|

|

|

Capítulo

II

Puente H.

Descripción

de la

arquitectura

del dispositivo puente H

.

|

|

|

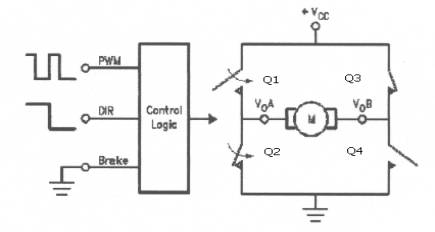

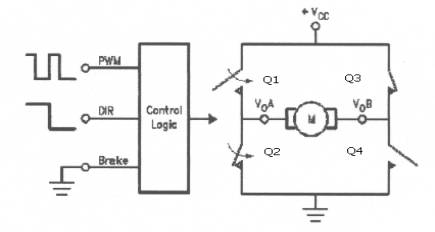

En la figura 2.6

se muestra la arquitectura equivalente mediante cuatro interruptores

del diseño conocido como puente " H ".

Este puente recibe una alimentación de DC y permite un

control bidireccional de la corriente que circula por el motor.

Figura

2.6 Puente H

|

|

|

|

|

|

Capítulo

III

Etapa de potencia.

Justificación.

|

|

| |

Los requerimientos de potencia de

nuestro trabajo están por

encima de las soluciones completamente integradas para el control de

motores de corriente continua, al superarse los 10 W que soporta esta

solución.

En consecuencia, la etapa de potencia

ha de ser construida con

componentes activos y discretos y dimensionados éstos para

atender los requerimientos previstos.

La topología no ofrece alternativa, una vez decidido el

controlador que la va a dirigir, el LM629, con salida PWM, por lo que

se diseñará un puente en H.

Igualmente sucede con los elementos de conmutación, que

entran en la gama de posibilidades de los MOSFET, no existiendo

necesidad de una potencia mayor que requiriera IGBT o conmutadores

controlados de mayor potencia.

El control del puente, proveniente del controlador, va a llevar el

disparo de los MOSFET mediante "drivers" integrados del tipo IR2110, de

"International Rectifiers", específico para este tipo de

aplicaciones, que soporta entrada PWM y salidas complementarias

referenciada a masa una y flotante la otra, para solventar los

problemas inherentes al referenciado del disparo en las

líneas de puerta no referenciadas a la masa de potencia, Q3

y Q1. También aporta una desactivación del puente

por exceso de corriente que proviene del "sensado" de la corriente de

la línea de potencia.

El proceso de selección de componentes del puente y su

dimensionado se detalla posteriormente.

A continuación se resume el funcionamiento básico

de esta topología.

Convertidor "Full-Bridge", puente completo (H).

Partiendo de una alimentación continua (potencia) aplicada

sobre Q1 (+) y Q2 (-) y aplicando señales de disparo a los

MOS FET, se pueden dar las siguientes situaciones:

1 Conducción de Q1 y Q4:

La carga inductiva se ve sometida a una tensión de magnitud

igual a la de la fuente, invertida en signo. Por ella circula una

corriente de sentido negativo respecto de la referencia.

2 Conducción de Q1 y Q3 o Q2 y Q4:

La carga resulta cortocircuitada, con tensión cero y sin

circulación de corriente.

4 Conducción de Q3 y Q4 o Q1 y Q2:

Estas situaciones resultan prohibidas, porque tienen como consecuencia

cortocircuitar la potencia.

Cuando aplicamos un control de puerta a los MOSFET en forma que

ésta sea la misma para Q2 y Q3 e igual pero complementaria

para Q1 y Q4, el circuito alternará el signo de

tensión y corriente siguiendo el ciclo de disparo (ciclo de

trabajo) sobre la carga. Al tratarse de una carga inductiva, y si el

ciclo de trabajo fue calculado para permitir la carga y descarga del

bobinado, a través de la carga circula una corriente media

que excitará el motor de forma proporcional al tiempo en que

resulten disparadas las líneas de MOSFET.

Con las combinaciones descritas anteriormente, fácilmente se

ve que, actuando sobre el disparo, podemos regular el nivel de la

corriente media de excitación del motor (velocidad) y su

sentido (sentido de giro). Igualmente se puede para el motor,

impidiendo que circule corriente por su bobinado. Este es el tipo de

control que precisa nuestra aplicación.

Concretando, al disponer de un control de disparo en forma de magnitud

y signo, lo que éste pretende es regular la velocidad

mediante el ancho del pulso considerado respecto de una frecuencia fija

(ciclo de trabajo) y su sentido de giro con la señal de

signo.

Consideraciones.

Se fijará una magnitud máxima de la

alimentación (potencia), que será la

máxima potencia del motor que podamos situar como carga.

Esta potencia máxima viene limitada por las prestaciones del

tipo de MOSFET seleccionado. Se determinarán las dimensiones

de diodos rápidos (Schotky) entre drenador y fuente de los

MOS FET, en función de los picos de tensión por

carga inductiva esperados.

Se fijará un ciclo de trabajo que también

tendrá un máximo, del orden de kilo hercios,

determinado por la capacidad de los MOSFET. Esta frecuencia

limitará también el tipo de carga que se pueda

situar, porque debe ser coherente con las características

inductivas del motor, en el sentido de que sus bobinados sean capaces

de seguir el ciclo de carga y descarga requerido. El ciclo de trabajo

se fijará mediante el reloj del controlador LM629. Esta

señal de control se conducirá al driver IR2110 a

través de opto acopladores, para evitar interferencias entre

el circuito lógico y el de potencia, aislándolos

entre sí.

Se fijarán unos "tiempos muertos" en los cuales no exista

excitación de puerta ninguna, durante las transiciones, para

dar tiempo a los MOSFET a alcanzar el estado requerido de

conducción o bloqueo, ya que su capacidad de entrada en

puerta retrasa su respuesta.

De lo contrario se producirán combinaciones indeseadas. Se

determinarán por las características de los

MOSFET y se fijarán en la entrada de los "drivers" IR2110

mediante una red R-C. Al tratarse de nano segundos, estos tiempos no

resultan significativos con respecto de la frecuencia de trabajo.

Se determinará el tipo y dimensionado de los disipadores de

los MOS FET para garantizar la potencia máxima fijada,

calculados sobre la impedancia térmica que suponga la

conmutación. La realimentación del sistema

tomará muestras de un "encoder" fijado sobre el rotor del

motor, conducida al controlador LM629 mediante "line drivers" de

línea diferencial.

Se tomará muestra del consumo de corriente del puente,

mediante sensado sobre la línea de retorno de potencia, para

controlar su magnitud máxima y media que será

tratada y digitalizada por un interfase diseñado al efecto,

para su lectura por el µC, con objeto de que éste

determine los límites de funcionamiento esperado y active

una protección si se ven superados.

Se establecerá un control de exceso de temperatura que se

tomará sobre el disipador de los MOSFET y

activará una interrupción del µC. Se

diseñará el interfase que conduzca esta

señal de interrupción.

Los requerimientos de potencia de

nuestro trabajo están por

encima de las soluciones completamente integradas para el control de

motores de corriente continua, al superarse los 10 W que soporta esta

solución.

|

|

|

|

|

|

|

|

|

Capítulo IV

Formas de señales del PWM

El

puente H, realiza la

interfaz fácilmente con diferentes formas de

señal PWM.

A

continuación se describen las dos formas más

populares de

PWM.

|

|

| |

1. Simple

señal de fase del PWM. Esta consiste de una simple

señal de una variable de ciclo obligado en la cual son en

codificadas ambas la dirección y la información

de la amplitud como se ve en la figura 2.6a.

Donde una señal PWM con un ciclo obligado del 50% representa

el manejo del cero, ya que el valor de la red de voltaje (integrada

sobre un período) entregado a la carga es cero.

|

|

|

|

Figuras

2.6a y 2.6b

|

| 2. Signo y

magnitud de PWM, consiste de una dirección separada y una

señal de amplitud ver figura 2.6b. La señal de

magnitud es modulada de ciclo obligado, y la ausencia de una

señal de pulso (una lógica continua de nivel

bajo), representa un manejo de cero. La corriente entregada a la carga

es proporcional al ancho de pulso. |

|

|

|

|

|

|

|

Capítulo

V

Limitación de corriente

El circuito de

protección para la limitación de corriente

será incorporado dentro del diseño del puente H.

|

|

Pero como

cualquier dispositivo de potencia, es importante que se considere el

efecto de la corriente que surge sustancialmente a través

del dispositivo. El sensado de corriente se tomara a través

de una resistencia de 0.1ohmio, este estará formado por un

"AO" del tipo LM 324 y este conectara a un comparador del tipo LM 311.

|

|

|

|

|

|

Semblanza

Breve

Semblanza

Breve

![]()