BAT49

Diodo SCHOTKY

|

| Como se ha

comentado anteriormente es el encargado de amortiguar los picos de

tensión, se usara el BAT49, que soporta una

tensión VRRM

de 80V. |

IR2110

High and Low side Driver

|

Son los encargados de

proporcionar el disparo inferior y superior de los MOSFET, la

circuitería que acompaña al driver es

típica para este tipo de montajes, teniendo en cuenta que

los condensadores, resistencias y diodos utilizados son los adecuados

para el disparo del MOSFET elegido.

Diodo se utilizara el D1N4148.

Resistencia utilizada de 22K.

Condensador utilizados de 0.1 y 1uF. |

LM324

Low Power Quad Operational Amplifiers

|

| Utilizado

como amplificador diferencial, amplificara la señal de

sesado

del puente H y la comunicara a un comparador que se detallara

seguidamente. |

LM311

Voltaje Comparator

|

| La salida de este

se aplicara a la función Shutdown del IR2110, esta

función apagara los transistores hasta la llegada del

siguiente

pulso, lo que permite un control de corriente ciclo por ciclo. |

74LS00

Quad 2-INPUT nand gate

|

| Esta compuesta por puertas Nand, Son las

encargadas de realizar las conexiones entre el LM629 salidas PWM y los

Octo acopladores, están llevaran una resistencia a su salida

para limetar la señal de los Octo acopladores. |

CD40106C

Hex Schmitt Trigger

|

| Es un circuito complementario

monolítico de Mos, construido con transistores de realce de

tipo N y de P, todas sus entradas están protegidas contra el

daño debido a las descargas estáticas, y es el

encargado de transmitir la señas de salida del los Octo

acopladores al circuito de potencia a través del los driver

IR2110. |

H11L1

Optoacopladores Logic Output

|

Opto

acopladores, son los encargados de aislar la parte de control de la de

potencia. Un octo acoplador combina un dispositivo semiconductor

formado por un foto emisor, un fotorreceptor y el camino por donde se

transmite la luz.

Todos estos elementos se encuentran

dentro de un encapsulado del tipo DIP.

La señal de entrada es

aplicada al foto emisor y la salida es tomada del foto rector.

Los opto acopladores convierten una

señal eléctrica en una señal luminosa

modulada y la vuelven a convertir en una señal

eléctrica, en ellos reside el aislamiento

eléctrico que pueden establecer entre circuitos.

La serie de H11L1 tiene un detector de

nivel alto con una velocidad optimizable junto a un diodo que emite

infrarrojos de arseniuro de galio, la salida incorpora un disparador de

Schimitt, que proporciona la histéresis para la inmunidad de

ruido y formar el pulso, utiliza una salida de colector abierto para la

flexibilidad máxima de su uso.

Algunas de sus

características:

- Alta tarifa de datos.

- Impulsión compatible con

microprocesadores.

- La salida compatible con la

lógica hunder 16mA en el máximo 0.4V

- Histéresis con./desc.

Garantizada en el umbral.

- Capacidad amplia del voltaje de

fuente, compatible con todos los sistemas populares de

lógica.

|

DS26LS31C / DS26LS32C

Line Drivers / Line receivers

|

| Estos dos componentes forman una parte muy

importante del circuito, auque no están representados en el

esquema, solamente hay una pequeña anotación,

ahora se intentara realizar una pequeña

aclaración ya que de ella puede partir el buen

funcionamiento entre el circuito y el motor a través del

Encoder. |

DS26LS32C

Quad High Speed Differentials

Line Receivers

|

El DS26LS32C son receptores

diferenciales de línea del cuadrángulo

diseñados para motores, el Rs-422 y el Rs-423 (Son

conductores de línea) se usan para la transmisión

de datos digitales equilibrada y desequilibrada.

Tiene una sensibilidad de entrada de 200

mV sobre una gama de voltajes de entrada de .

Tiene incorporados los resistores

pull-down que previenen la oscilación de la salida en los

canales insusitados.

Las salidas de triple estado del TM, con

la opción de la salida complementaria permiten para recibir

directamente sobre un BUS de datos.

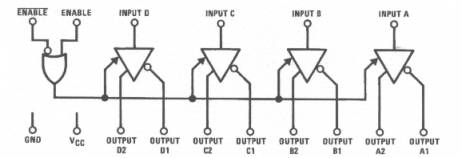

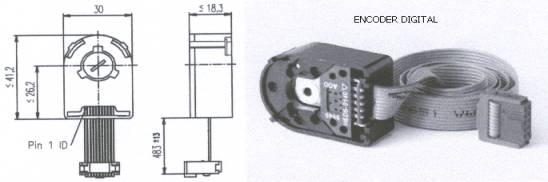

En la figura siguiente podemos ver el

diagrama lógico.

|

DS26LS31C

Quad High Speed Differentials

Line Drivers

|

El DS26LS31C es un conductor de

línea diferencial del cuadrángulo para

líneas equilibradas de datos del excedente digital de la

transmisión, se diseña para proporcionar la

impulsión diferenciada unipolar a las líneas de

conductor de doble retorcido o de alambres paralelos de la

transmisión.

El circuito proporciona un permitir e

inhabilita la función a los cuatro conductores de

transmisión.

Ofrece salidas de triple estado y

lógicamente las salidas complementarias de AND, las entradas

son todas de LS compatibles.

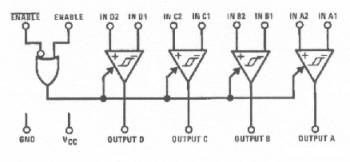

En la figura siguiente podemos ver el

diagrama lógico.

|

Entre estos dos dispositivos

estará conectada una línea de impedancia, esta

distancia va a depender de la situación que tengamos entre

el circuito y el Encoder.

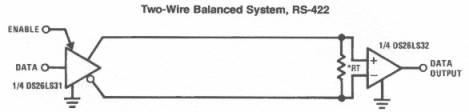

En la siguiente figura se puede ver la conexión de la

línea RS-422 entre los dispositivos.

En la figura solo se muestra una

línea, en nuestro proyecto a desarrollar estará

compuesta

por tres líneas que va a conexionar el dispositivo LM629,

entradas A, B, In del Encoder con las salidas del propio Encoder

situado en el eje del motor, como podemos comprobar en la figura

siguiente:

RT

es la resistencia Pull-down. Su valor va a depender de la distancia de

la línea.

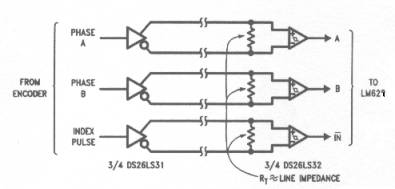

Existen líneas de impedancia ya constituidas formadas por el

Encoder digital y el propio ds26ls31c, como se muestra en la figura

siguiente.

|

IRPF250N

MOSFET

|

| Transistor MOSFET, son los

que actúan como interruptores y dan paso al funcionamiento

del motor DC. |

AD536A

Convertidor de valor eficaz a continuo

|

| El AD536 computa

directamente el valor eficaz de una señal compleja de

entrada

conteniendo componentes de alterna (AC) y continua (DC).

Las

pérdidas de alimentación con las entradas

conectadas no causan fallo en la unidad.

Las entradas y salidas están completamente protegidas.

Tiene un ancho de banda de 300 khz con

3dB de error para señales de un nivel de 100 mV.

Descripción de funcionamiento.

El AD536 computa el verdadero valor

medio cuadrático de una señal AC ó (AC

+ DC), dando en su salida un nivel equivalente en DC.

El único componente externo

requerido para desarrollar las medidas con la completa

precisión especificada es el condensador, el cual completa

el periodo promedio.

El valor de este condensador determina

la precisión en baja frecuencia AC, nivel de rizado y el

tiempo de establecimiento.

Diferentes configuraciones.

*nota: Las figuras sobre las que se

hará alusión se encuentra en el apartado de anexo

A.

( Figura 1 (Configuración con

alimentación simétrica +VS y -VS)

Mide el valor eficaz de una

señal AC y DC presente en la entrada. Mostrará un

error para bajas frecuencias de entrada como una función del

filtro capacitivo Cav.

( Figura 3 (Configuración con

alimentación referenciada a masa. Tensión de 5 a

36 Voltios)

Si se desea rechazar la entrada DC, un

condensador es añadido en serie con la entrada.

El condensador debe ser sin polaridad.

Es aconsejable colocar en alimentación un condensador

cerámico de 0.1 µF a masa tan cerca del

dispositivo como sea posible.

La mayor limitación de esta

conexión es que únicamente las señales

AC pueden ser medidas, ya que el estado de la entrada diferencial se

debe separar de masa para una operación correcta.

En la figura 5, se puede apreciar en la

gráfica la elección de diferentes condensadores

Cav según la frecuencia de trabajo.

( Figura 7 (Configuración

elegida para el proyecto)

El mejor método para reducir

el rizado de salida es el uso de un POST-FILTER.

Si un único filtro polo es

usado (C3 quitado, RX corto), y C2 es aproximadamente 2 X Cav, el

rizado es reducido y el tiempo de establecimiento es incrementado (Ver

figura 8, por ejemplo Cav = 1µF, C2 = 2.2 µF y F =

60 Hz, el rizado se reduce del 10% al 0.3%, aunque el tiempo es

incrementado por un factor de 3. Cav y C2 pueden ser reducidos para

realizar la compensación deseada.

Con dos polos PST-FILTER, el error de

rizado se reduce aún bastante más y el tiempo

apenas sube respecto al de un polo-filtro, por ello hemos elegido dicha

configuración.

*Para todas las configuraciones se

utiliza:

VRms = Aug [Vin² / Vrms]

Vout = 2 R2 * Irms = Vin rms

|

OP07

Amplificador Operacional

|

Amplificador operacional de

alta gama porque nos ofrece:

* Bajísima

dependencia de sus características frente a la temperatura.

* Bajísima

tensión de offset.

* Bajísimo

ruido.

* Bajísima

deriva de la tensión de offset con la temperatura.

Se utilizara como se ha dicho anteriormente en dos configuraciones,

como comparador y como filtro paso bajo |

MM74HC76

Dual JK Flip-flop With Set And Clear

|

Estas básculas utilizan

tecnología microCMOS, que permite:

Alta velocidad (30 MHz

mínimo).

Bajo consumo.

Alta inmunidad al ruido.

Todas las entradas están

protegidas del peligro por descargas electroestáticas.

Descripción de funcionamiento.

Cada báscula (flip-flop)

tiene entradas independientes J, K, PRESET, CLEAR y DE RELOJ, salidas Q

y ^Q. Estos dispositivos son atacados con flancos en la entrada de

reloj y cambian de estado en la transición negativa del

pulso de reloj.

Clear y Preset son independientes del

reloj y son ejecutados por un nivel lógico bajo en la

entrada correspondiente.

Este dispositivo se utilizara en el

circuito de señales de reloj para obtener diferentes

frecuencias de reloj.

Con el estará

acompañado varias puertas AND de dos y tres entrada como son

:

MM74HC11, AND de tres entradas.

MM74HC08, AND de dos entradas.

|

ADC0808

Converters with 8-channel Multiplexer

|

El

componente de adquisición de datos ADC0808, es un

dispositivo CMOS monolítico con un convertidor

analógico-digital de 8 bits, multiplexor de 8 canales y

lógica de control compatible con microprocesador.

El convertidor

analógico-digital de 8 bits utiliza aproximaciones sucesivas

como técnica de conversión.

Éste tiene como

característica un comparador estabilizado con un chopeado de

alta impedancia, un divisor de tensión con 256R con un

árbol de conmutación analógico y un

registro de aproximaciones sucesivas.

El multiplexor de 8 canales puede

acceder directamente a cualquiera de las 8 señales

analógicas por separado.

El dispositivo elimina la necesidad de

ajuste de 0 y escala completa externos. Fácil

conexión con microprocesadores, se da por los multiplexores

latcheados y sus entradas de direcciones decodificadas y salidas

latcheados TTL-Triestado.

El diseño del ADC0808 ha sido

optimizado incorporando los aspectos más deseables de varias

técnicas de conversión

analógico-digital.

El ADC0808 ofrece: alta velocidad,

influencia mínima de la temperatura sobre su funcionamiento

y consumo de potencia mínimo.

Descripción funcional.

El dispositivo contiene un multiplexor

de 8 señales analógicas por separado. Una

particular entrada del canal es seleccionada usando el decodificador de

direcciones.

(Ver tabla 1, que muestra el estado de

las líneas para seleccionar cualquiera de las

entradas).

La

monotonicidad es particularmente importante en el control de sistemas

con realimentación en lazo cerrado. Una relación

no monótona puede producir oscilaciones, que

serán catastróficas para el sistema.

Un proceso de conversión se

verá interrumpido al recibir un nuevo pulso de comienzo de

conversión.

La conversión continua se

puede realizar llevando la salida final de conversión (EOC)

a la entrada (SC).

Si se usa de este modo, un pulso externo

de comienzo de conversión se deberá aplicar

después del encendido.

El comparador de chopeado estabilizado,

convierte la señal de entrada DC (continua) en una

señal AC (alterna), esta señal se lleva luego a

un amplificador AC de alta ganancia y se le restaura el nivel DC.

Esta técnica limita la deriva

de los componentes del amplificador, ya que lo que se deriva es un

componente DC, que no se pasa por el amplificador de AC.

Esto hace que el convertidor entero

analógico-digital sea extremadamente insensible a la

temperatura, a fallos con el tiempo y errores por el offset de entrada.

| Selección

canal analógico |

Líneas

de dirección |

|

C |

B |

A |

| IN0 |

L |

L |

L |

| IN1 |

L |

L |

H |

| IN2 |

L |

H |

L |

| IN3 |

L |

H |

H |

| IN4 |

H |

L |

L |

| IN5 |

H |

L |

H |

| IN6 |

H |

H |

L |

| IN7 |

H |

H |

H |

|

| Tabla

1 Estado de las líneas

para seleccionar cualquiera de las entradas |

SN74HC4040

Divisor de frecuencia

|

| Este dispositivo nos

proporcionara las frecuencias requerida en nuestro sistema. |

STDGC

16Mhz

|

| Este dispositivo nos

proporciona la señal de 16Mhz para nuestro sistema.

|

LM7476A

Decodificador BCD de 7 segmentos

|

| Este dispositivo,

es el encargado de proporcionar las señales al Displey de 7

segmentos, se caracteriza por tener las salida a nivel bajo. |

DISPLAY

7 Segmentos, de anodo comun

|

| En el se representaran los

errores producidos en nuestro sistema, cada numero significara un error

determinado. |

TL7705A

Power-Supply Monitor with reset

|

| Este sistema en aplicaciones

con microprocesadores con entrada de reset, se utilizara para efectuar

el reset a nuestro circuito. |

To220 (212-829)

TERMICO Normally closed

|

| Este dispositivo

esta basado en un interruptor térmico, actúa por

el

aumento de temperatura, se utiliza la serie 212-829 en el cual el

contacto térmico esta normalmente cerrado. |

MGDI-18 : 18W POWER (+ 5V)

MGDI-19 : 20W POWER (± 15V)

|

| Dadas las

especificaciones de nuestro trabajo, se tendrá una

alimentaron

de 25v y esta se aprovechara a través de los convertidores

utilizados para la alimentación de todo el sistema. |

| |

| Nota: Las

características de operación de los diferentes

elementos,

se pueden consultar en el Anexo A. ( Cd-rom adjunto). |

| |

|

|

Semblanza

Breve

Semblanza

Breve

![]()